雷锋网 AI 科技评论按: 说起 FPGA,很多人能够都不熟习,它的英文全称为 Field Programmable Gate Array,即现场可编程门阵列,也被称为可编程集成电路。随着大数据以及 AI 的开展,越来越多的数据中心引入 FPGA 作为 CPU 的减速器以进步数据处置速度,提升效劳器功能,因而降低 FPGA 的能耗也成为数据中心里新的应战。本文引对于互联网金融P2P企业来说,支付市场完善的标准和管理系统将彻底改变互联网金融行业的格局,不仅给从业者提供了的巨大的发展机遇,也带来了全新的挑战。见了其中一种降低 FPGA 能耗的办法——基于自测量的 FPGA 静态电压调理处理方案。本文依据嘉宾的直播分享整理而成。

静态电压调理(DVS)作为罕见的数字芯片节能技术,曾经少量使用于 CPU 或 GPU 等芯片中。由于 FPGA 共同的可编程硬件构造,它们的片上电路随使用的改动而改动,这为 FPGA 的静态电压调理带来了极大的困难。来自多伦多大学电子系的在读博士生赵舒泽为此提出了一种新的改良方案,无效地降低了芯片能耗并提升了功能。

赵舒泽,浙江大学电气工程学院电力电子方向学士,多伦多大学电子系硕士,多伦多大学电子系博士在读。研讨方向为 LED 光通讯,谐振变流器,变流器的数字控制,以及电力电子在数据中心的使用。

分享提纲:

FPGA的简介,FPGA的片上构造

FPGA的能耗

基于自测量的FPGA静态电压调理(DVS)

分享内容:

大家好,我是赵舒泽,明天分享的内容是硬件方面我们的一些研讨效果。接上去首先为大家复杂引见一下数据中心的构造以及能耗的成绩,然后是关于 FPGA 的简介以及 FPGA 在能耗上的应战。最初为大家引见的是我们团队的研讨效果,即如何在 FPGA 上完成静态电压的调理。

数据中心的能耗

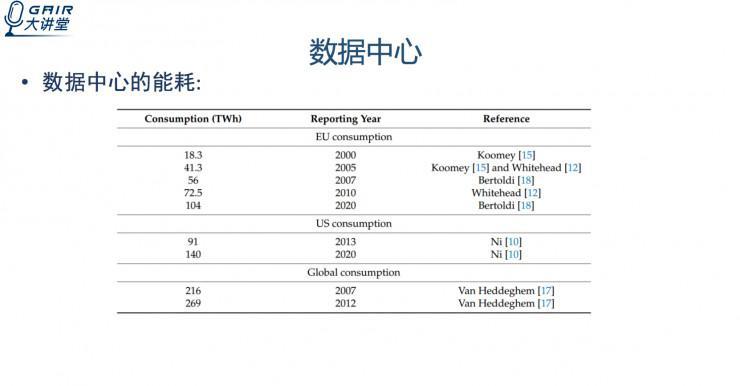

近十几年,随着信息技术的开展,尤其是最近十分火的大数据、云计算、人工智能等这些方向的停顿,数据中心作为这些完成这些使用面前的大脑,无疑也是阅历了高速开展。随着数据中心的集成度,计算才能的进步,数据中心的能耗也不断是一个十分顺手的成绩。

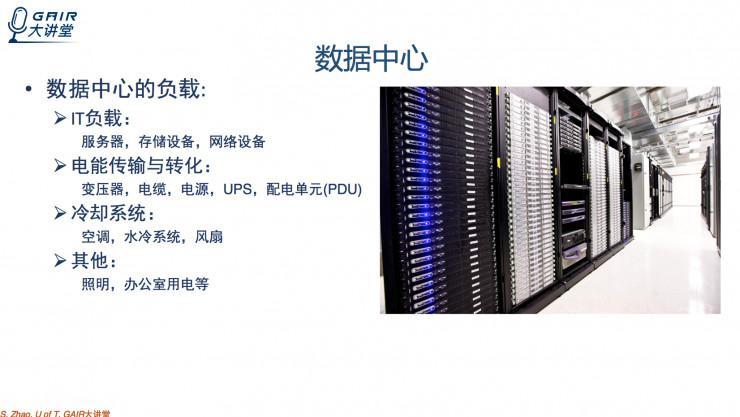

以美国为例,2013 年数据中心的总能耗估量是 91 太瓦时(TWh),相当于一个中等国度(例如菲律宾)全国的总用电量。要处理能耗成绩,首先要看一下一个数据中心有哪些用电负载。

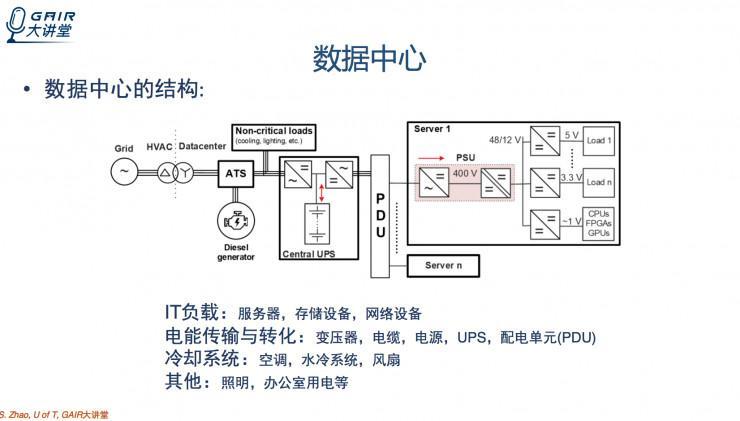

可以大致总结为四类:IT 负载,包括效劳器,存储设备,网络设备,交流机等;电能传输与转化,包括变压器,电缆,电源,UPS,配电单元等带来的损耗;冷却零碎,包括空调,水冷零碎,风扇等。其他,包括照明,办公室用电等。

数据中心的构造

「ATS 自动转化开关」的目的是:在电网呈现成绩时,可以自动转换到柴油发电机组,这样可以保证负载端不会呈现断电的状况。

「中心 UPS」有两方面的作用。一方面可以保证保送高质量的电能给IT负载,另一方面,在呈现断电的状况下,柴油发电机还需求一定的启动工夫,这段空档由 UPS 来暂时供电,保证负载不会呈现断电的状况。

数据中心的能耗构造

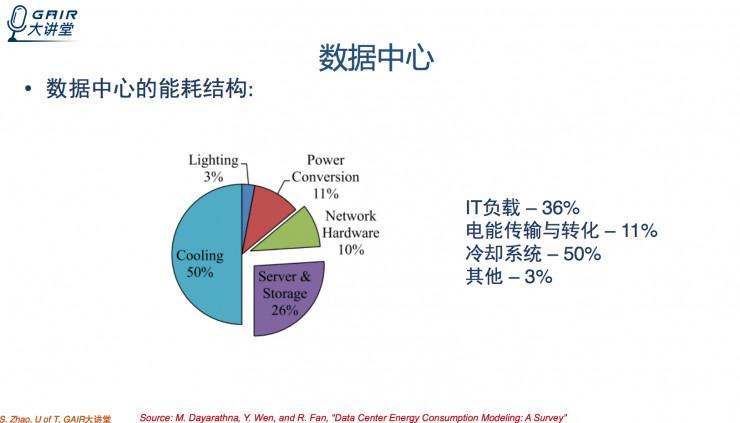

每个数据中心的能耗其实很不同,这个图只是一个均匀值。IT 负载其实只占到 36% 的能耗,电能传输与转化大约占 11%。其他有一半能耗都是被冷却零碎用掉的。也就是说为了冷却 IT 负载和电能传输与转化所发生的热能,需求耗费等量甚至更多的能量来冷却数据中心,以保证正常任务。

如何降低IT负载中FPGA的能耗

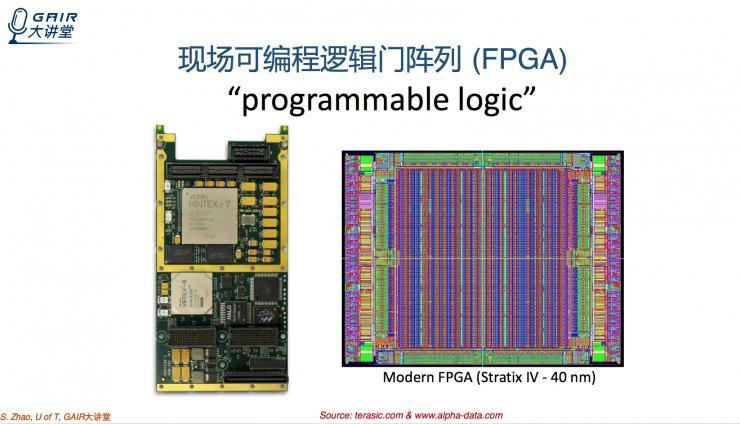

FPGA 的中文称号为现场可编程逻辑门阵列。FPGA 在过来少量使用在消费电子产品,无线基站,军事,医疗等高端使用场所里,随着大数据,人工智能的疾速开展,我们对效劳器的呼应速度的要求不时进步,CPU 曾经被证明不太合适停止少量浮点运算,而 FPGA 的片上电路是可编程的,开发工夫比拟短,可以灵敏的部署并且可以完成大规模的并行计算。由于这些缘由,它开端被少量部署在数据中心里作为 CPU 的减速器,协助数据处置以及计算,包括协助网络通讯等等。

FPGA的优势和优势

关于 CPU/MCU 这样基于指令集的芯片来说,FPGA 有更大的灵敏性,另外由于它是可编程的,可用最复杂的硬件架构来完成所需求的逻辑功用,因而更节省动力。

缺陷是,在和特种芯片 ASIC 相比,速度较慢,能耗更高。ASIC 芯片外部架构虽较为复杂,不可以硬件编程,只能用来专门处置某一种功用,灵敏性最差,但是在执行某一种义务上的效率最高。

FPGA 芯片外部架构略微复杂一些,可以硬件编程,因此可以经过硬件编程言语来改动外部芯片的逻辑构造,从而可以在提供一定灵敏性的同时,还可以保证较高的处置效率,算是在灵敏性和功能上取了个折中。

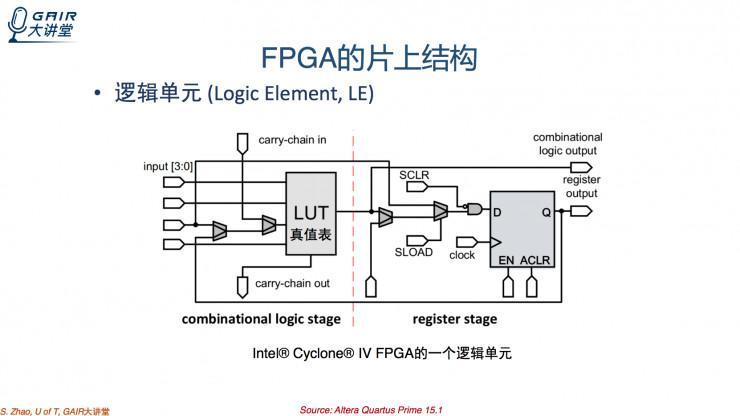

FPGA的片上构造

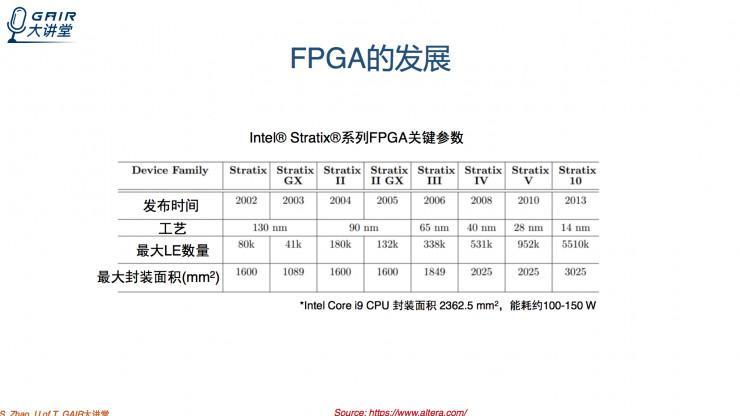

FPGA的开展

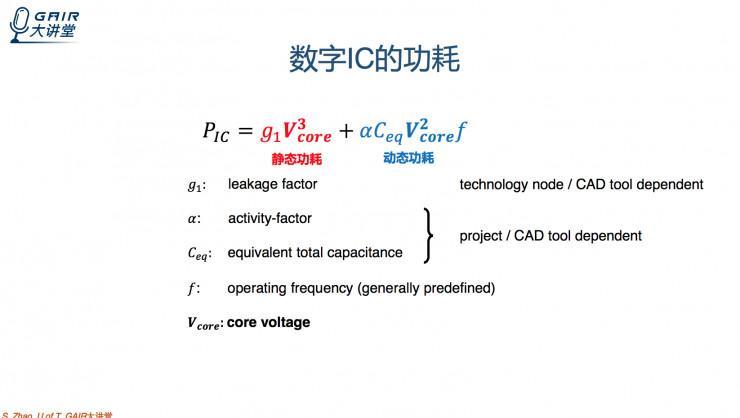

数字IC的功耗

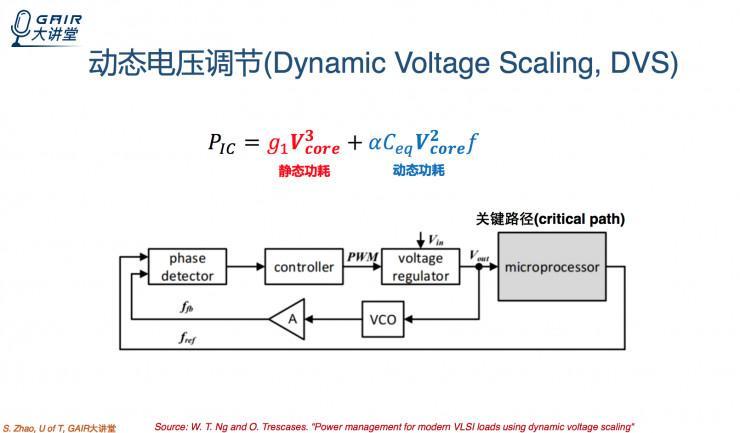

静态电压调理

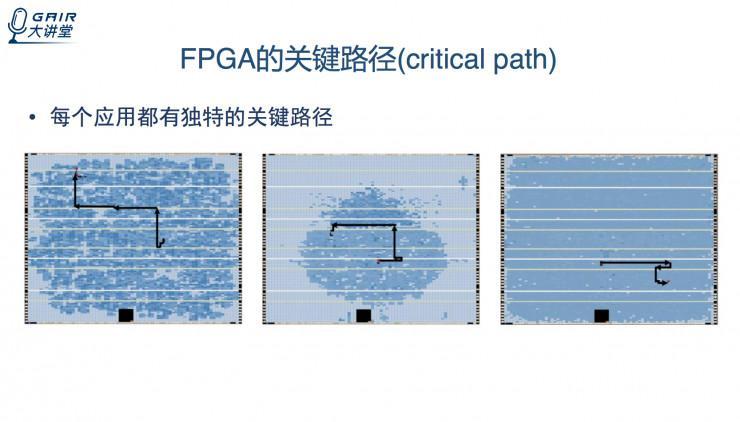

FPGA的关键途径

每个使用都有共同的关键途径

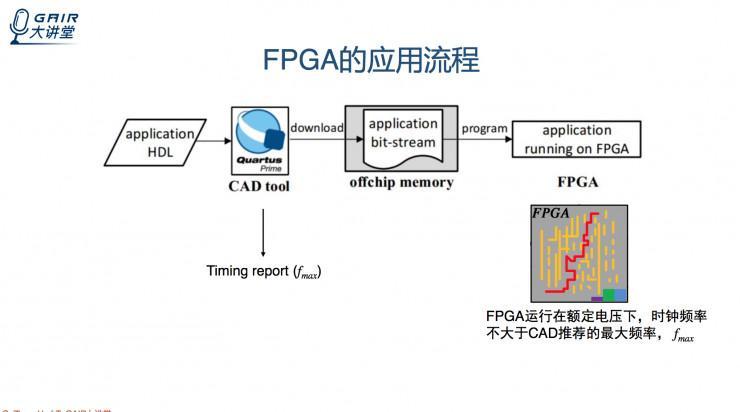

FPGA的使用流程

FPGA的的静态电压调理

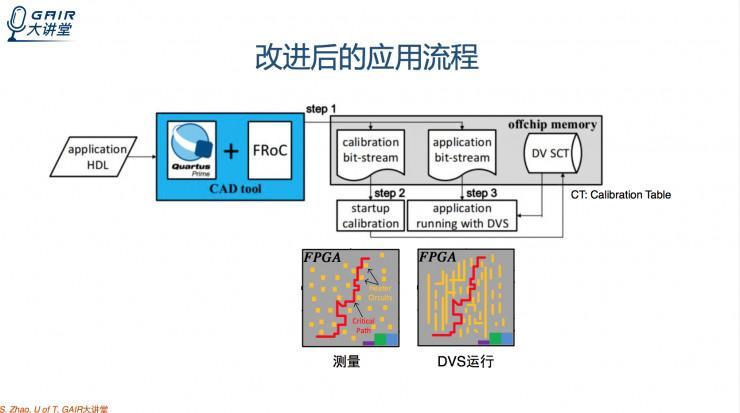

我们的思绪是: FPGA 有不确定的片上构造,但是可以反复烧制。我们应用这个特点,把每一次的关键途径都提早提取出来,把这些关键途径独自烧制在 FPGA 上,先测量这些关键途径的延迟有多少,测完后把这些数据放在片外的存储器里。之后再将FPGA烧入用户的使用,静态电压调理的控制模块会从刚测到的数据中找到以后温度和频率下最低的供电电压是多少,然后电源依照这个电压来给 FPGA 来供电。

改良后的使用流程

完好的流程图解读请看视频回放。

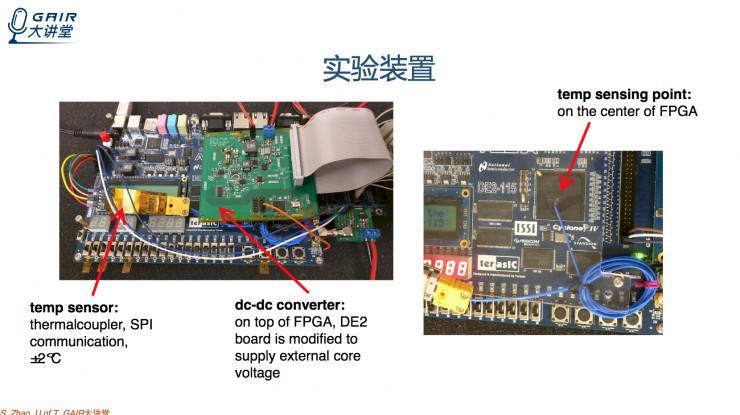

实验安装

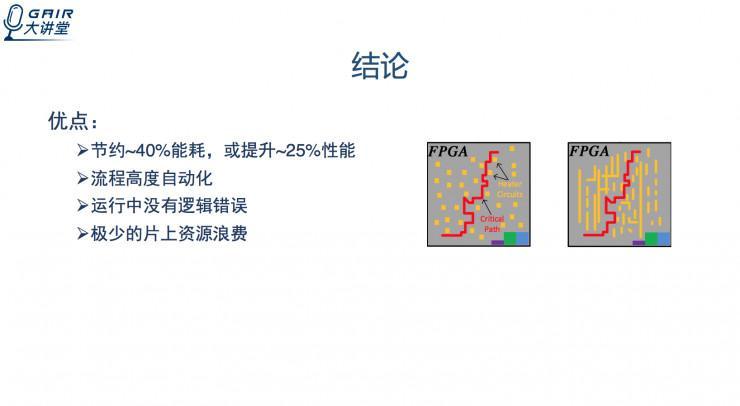

实验结论

雷锋网提供实验流程及详细细节引荐观看AI慕课学院: FPGA的静态电压调理(DVS)——谈谈数据中心里FPGA的节能。

微信大众号:「AI 研习社」临时提供收费视频直播课程,欢送关注!

雷锋网 (大众号:雷锋网)

。